# Introduction

Creating an X-BLOX Design

Processing Your Design

Module Definitions

X-BLOX User Guide

X-BLOX-Generated RPMs

**Understanding X-BLOX Operations**

Command and Option Syntax

Index

**₹XILINX\***, XACT, XC2064, XC3090, XC4005, and XC-DS501 are registered trademarks of Xilinx. All XC-prefix product designations, XACT-Performance, XAPP, X-BLOX, XChecker, XDM, XDS, XEPLD, XFT, XPP, XSI, BITA, Configurable Logic Cell, CLC, Dual Block, FastCLK, HardWire, LCA, Logic Cell, LogicProfessor, MicroVia, PLUSASM, UIM, VectorMaze, and ZERO+ are trademarks of Xilinx. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx.

IBM is a registered trademark and PC/AT, PC/XT, PS/2 and Micro Channel are trademarks of International Business Machines Corporation. DASH, Data I/O and FutureNet are registered trademarks and ABEL, ABEL-HDL and ABEL-PLA are trademarks of Data I/O Corporation. SimuCad and Silos are registered trademarks and P-Silos and P/C-Silos are trademarks of SimuCad Corporation. Microsoft is a registered trademark and MS-DOS is a trademark of Microsoft Corporation. Centronics is a registered trademark of Centronics Data Computer Corporation. PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc. UNIX is a trademark of AT&T Technologies, Inc. CUPL is a trademark of Logical Devices, Inc. Apollo and AEGIS are registered trademarks of Hewlett-Packard Corporation. Mentor and IDEA are registered trademarks and NETED, Design Architect, QuickSim, QuickSim II, and EXPAND are trademarks of Mentor Graphics, Inc. Sun is a registered trademark of Sun Microsystems, Inc. SCHEMA III+ and SCHEMA III are trademarks of Omation Corporation. OrCAD is a registered trademark of OrCAD Systems Corporation. Viewlogic, Viewsim, and Viewdraw are registered trademarks of Viewlogic Systems, Inc. CASE Technology is a trademark of Digital Equipment Corporation. Synopsys is a registered trademark of Synopsys, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc.

Xilinx does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. cannot assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx products are protected under at least the following U.S. patent: 5,224,056. Xilinx, Inc. does not represent that Xilinx products are free from patent infringement or from any other third-party right. Xilinx assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not be liable for the accuracy or correctness of any engineering or software or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

# **Preface**

### **About This Manual**

This manual describes Xilinx's X-BLOX<sup>TM</sup> library and software, which are used for designing XC3000A/L, XC3100A, and XC4000 FPGA families.

Before using this manual, you should be familiar with the operations that are common to all Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *XACT Reference Guide*.

Other publications you can consult for related information are the *XACT Libraries Guide*, the *XACT User Guide*, and your design interface user guide.

# **Manual Contents**

This manual covers the following topics.

- Chapter 1, INTRODUCTION, introduces X-BLOX, its features, and capabilities.

- Chapter 2, CREATING AN X-BLOX DESIGN, discusses the X-BLOX library of modules and how to customize these modules using attributes and buses.

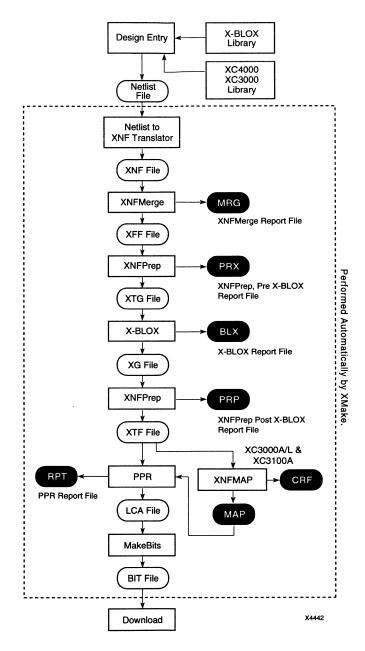

- Chapter 3, PROCESSING YOUR DESIGN, outlines the specific procedures you should use for design creation, implementation, and simulation on three supported third-party tools: Viewlogic, Mentor, and OrCAD.

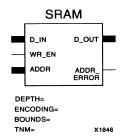

- Chapter 4, MODULE DEFINITIONS, describes X-BLOX modules individually and provides the attribute and syntax information required to use the modules.

- Chapter 5, X-BLOX-GENERATED RELATIONALLY PLACED MACROS, discusses how X-BLOX synthesizes specific modules into RPMs.

- Chapter 6, UNDERSTANDING X-BLOX OPERATIONS, explains the operations that X-BLOX performs when it processes your design for implementation or simulation.

- Appendix A, COMMAND AND OPTION SYNTAX, provides the syntax for executing X-BLOX as a stand-alone program, the options you can use to modify the way this program executes, and the files used or created by X-BLOX.

# **Conventions**

The following conventions are used in this manual's syntactical statements:

| Courier<br>regular | font | System messages or program files appear in regular Courier font.                                                           |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------|

| Courier<br>bold    | font | Literal commands that you must enter in syntax statements are in bold Courier font.                                        |

| italic font        |      | Variables that you replace in syntax statements are in italic font.                                                        |

| [ ]                |      | Square brackets denote optional items or parameters. However, in bus specifications, such as bus [7:0], they are required. |

| { }                |      | Braces enclose a list of items from which you must choose one or more.                                                     |

|                    |      | A vertical ellipsis indicates material that has been omitted.                                                              |

| •••                |      | A horizontal ellipsis indicates that the preceding can be repeated one or more times.                                      |

| 1                  |      | A vertical bar separates items in a list of choices.                                                                       |

| 4                  |      | This symbol denotes a carriage return.                                                                                     |

# **Contents**

| Chapter 1 | Introduction                                          |      |

|-----------|-------------------------------------------------------|------|

|           | X-BLOX Features                                       | 1-1  |

|           | X-BLOX Design Examples Directory                      | 1-2  |

| Chapter 2 | Creating an X-BLOX Design                             |      |

|           | Adding an X-BLOX Module to Your Schematic             | 2-1  |

|           | Customizing an X-BLOX Module                          |      |

|           | Implementation Styles and Operating Modes             | 2-4  |

|           | Operating Modes                                       | 2-6  |

|           | Data Values                                           |      |

|           | Synchronous and Asynchronous Control                  | 2-8  |

|           | Power-up Reset and Initialization                     |      |

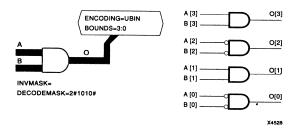

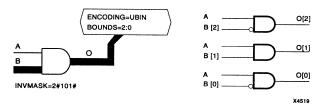

|           | Inverting and Decoding Masks for Bused Gate Functions |      |

|           | INVMASK and DECODEMASK Attributes                     |      |

|           | Single-Input Bused Modules                            |      |

|           | Double-Input Bused Modules                            |      |

|           | Single-Bus Gated Modules                              |      |

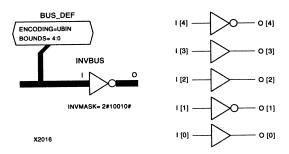

|           | INVBUS Module                                         |      |

|           | Pull-up and Pull-down Resistors for I/O Pads          |      |

|           | FLOAT_VAL Attribute                                   |      |

|           | Out-of-Range Indicators                               |      |

|           | Representing X-BLOX Buses                             |      |

|           | Specifying Buses and Bus Labels                       |      |

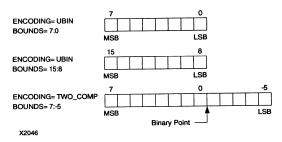

|           | Bus Data Types                                        |      |

|           | ENCODING                                              |      |

|           | BOUNDS                                                |      |

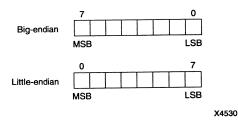

|           | Big-Endian vs. Little-Endian                          |      |

|           | Data Type Propagation                                 |      |

|           | Creating a Hierarchical Symbol                        |      |

|           | Bus Sizes                                             |      |

|           | Data Types                                            |      |

|           | Data Type Propagation                                 |      |

|           | Signal Aliasing                                       |      |

|           | Bus Manipulation                                      | 2-25 |

|           | CAST Symbol                                                                                                                                                                                                                                                                    | 2-26<br>2-26<br>2-27<br>2-27<br>2-27<br>2-28<br>2-29<br>2-30<br>2-31      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Chapter 3 | Processing Your Design                                                                                                                                                                                                                                                         |                                                                           |

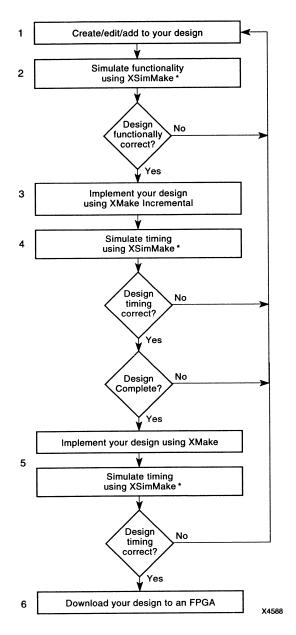

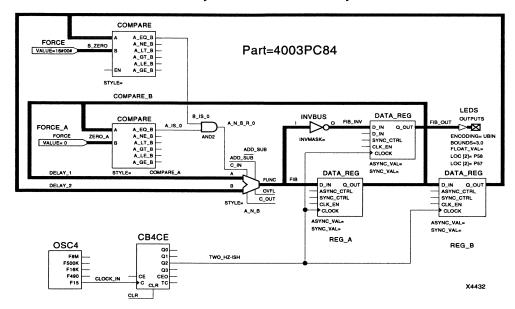

|           | Step 1: Creating and Modifying Your Design Step 2: Performing Functional Simulation Step 3: Implementing a Partial Design Step 4: Performing Timing Simulation Step 5: Implementing the Complete Design Step 6: Downloading Your Design X-BLOX Design Example Design Procedure | 3-8<br>3-10<br>3-12<br>3-14<br>3-14<br>3-15                               |

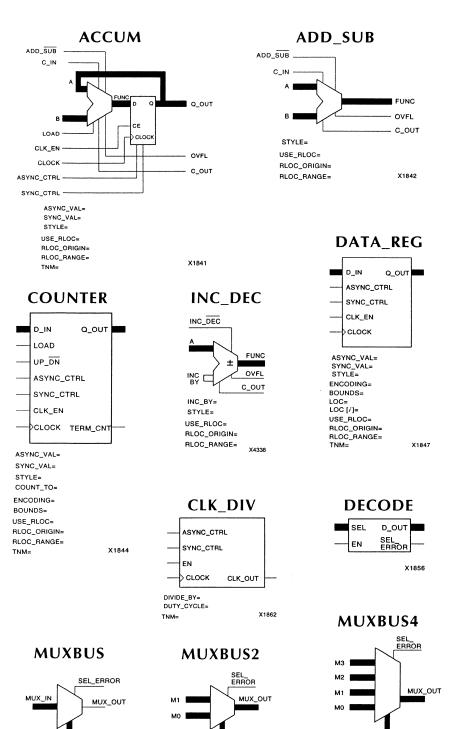

| Chapter 4 | Module Definitions                                                                                                                                                                                                                                                             |                                                                           |

|           | Bused Gate Functions                                                                                                                                                                                                                                                           | 4-3<br>4-8<br>4-9<br>4-11<br>4-14<br>4-15<br>4-15<br>4-19<br>4-19<br>4-21 |

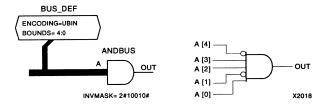

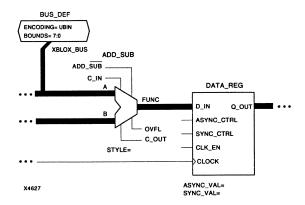

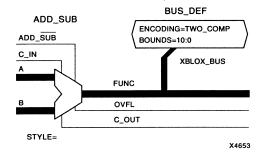

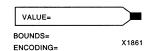

|           | BUS_DEF — Bus Data-Type Definition                                                                                                                                                                                                                                             |                                                                           |

| Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-22 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

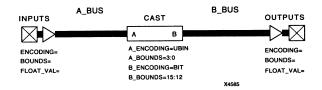

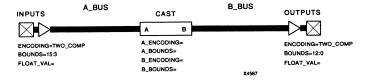

| CAST — Data Type Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-24 |

| Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-24 |

| Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-27 |

| Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-27 |

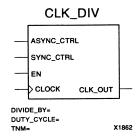

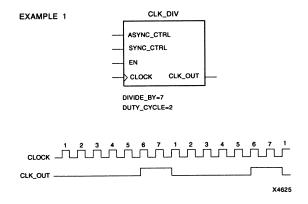

| CLK_DIV — Clock or Frequency Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-28 |

| Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-29 |

| Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-29 |

| Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-30 |

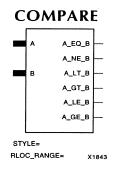

| COMPARE — Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-32 |

| Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-32 |

| Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

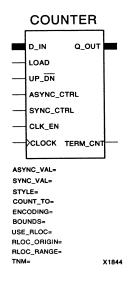

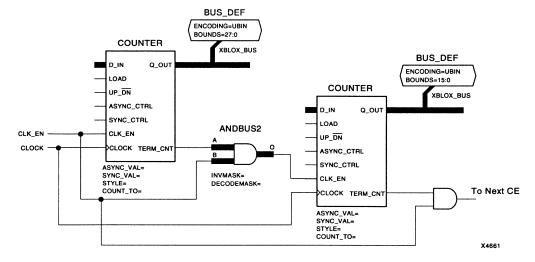

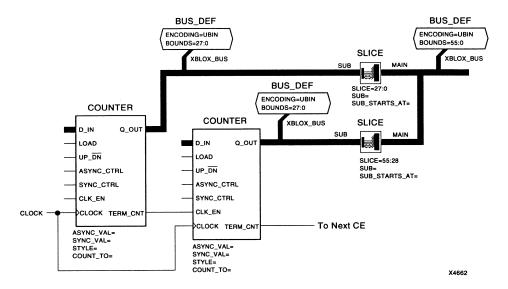

| COUNTER — Universal Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-36 |

| Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-37 |

| Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-38 |

| Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Counter Style Features and Selection Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| BINARÝ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| JOHNSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| LFSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| ONE_HOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-44 |

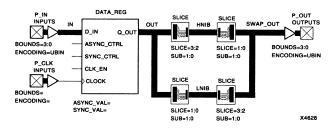

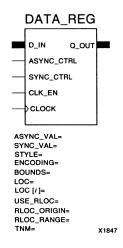

| DATA_REG — Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-50 |

| Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-50 |

| STYLE Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-52 |

| Conditions for Implementation in an IOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

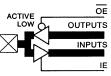

| DECODE — 1-of-n Decoder/Demultiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-58 |

| Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |